Part Number:DRV8308

We are having trouble limiting the startup current with Clock Frequency Mode.

Our startup can peak as up as 24A depending on motor and input voltage configuration (24V+-10%)

According to the data sheet, the SPEED register should adjust the open loop gain before Lock, but in our tests it actuality apply a gain in CLKIN resulting in a lower speed after LOCKn, and do not affect to the start current.

Our Risense is 0,02 ohms

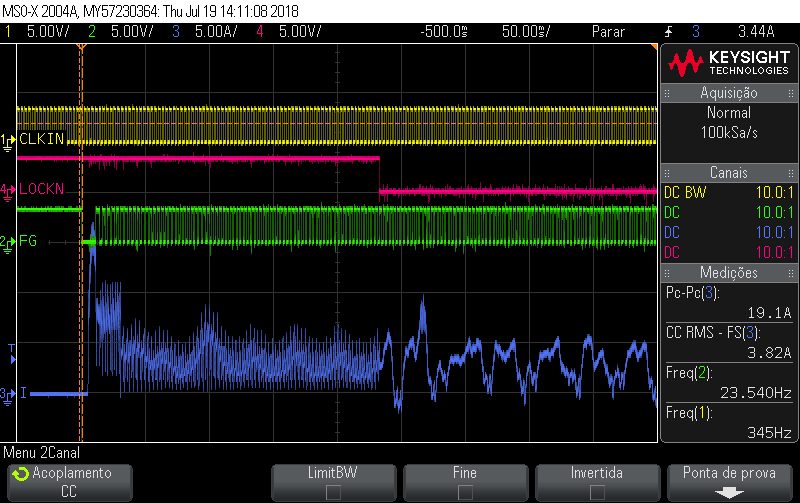

Here follow a 17A peak example, best result reached so far:

Our register configuration:

drive,speed_mode=<0>; /* closed loop mode*/

drive,pwmf = <2>; /* external FET Pwm frequency 100Khz*/

drive,fgsel= <1>; /* xor all 3 hall sensor */

drive,aa_setpt = <5>; /* ~95Hz */

drive,ag_setpt = <7>; /* ~382Hz */

drive,advance = <43>; /* ADVANCE */

drive,minspd = <5>; /* Minimal speed for lock */

drive,spdrevs = <20>; /* Hall Us required for lock */

drive,mod120 = <3970>; /* fixed for closed loop mode */

drive,intclk = <5>; /* Integrator clock */

drive,spdgain = <11>; /* closed loop gain */

drive,filk1 = <1200>; /* FILK1 */

drive,filk2 = <950>; /* FILK2 */

drive,cmpk1 = <280>; /* CMPK1 */

drive,cmpk2 = <560>; /* CMPK2 */

drive,loop_gain = <240>; /* closed loop gain */

drive,speed = <2000>; /* open loop gain ???*/

SPI write debug to confirm the data:

reg00 = [71] [84]

reg01 = [00] [2b]

reg02 = [14] [05]

reg03 = [6f] [82]

reg04 = [01] [43]

reg05 = [50] [0b]

reg06 = [04] [b0]

reg07 = [03] [b6]

reg08 = [01] [18]

reg09 = [52] [30]

reg0a = [f0] [f0]

reg0b = [07] [d0]

reg2a = [00] [00]

Any Idea to what